# VerSyKo

Verifikation von Systemen synchroner Software-Komponenten Verification of Systems With Synchronous Software Components

Contract Specification and Domain Specific Modeling Language for GALS Systems An Approach to System Validation

Version of 24. Juni 2013

Verified Systems International GmbH

Informatik Consulting Systems AG

Institut für Theoretische Information, Technische Universität Braunschweig

Das diesem Bericht zugrunde liegende Vorhaben wurde mit Mitteln des Bundesministeriums für Bildung und Forschung unter dem Förderkennzeichen 01IS10050A, 01IS10050B, 01IS10050C gefördert. Die Verantwortung für den Inhalt dieser Veröffentlichung liegt bei den Autoren.

# **Contents**

| 1 | Intr | Introduction                                                                 |    |  |  |  |  |

|---|------|------------------------------------------------------------------------------|----|--|--|--|--|

|   | 1.1  | Problem description and main goals                                           | 1  |  |  |  |  |

|   | 1.2  | Overview of main concepts/tools developed by VerSyKo                         | 2  |  |  |  |  |

|   | 1.3  | Related Work                                                                 | 5  |  |  |  |  |

| 2 | Prer | Prerequisites                                                                |    |  |  |  |  |

|   | 2.1  | SCADE                                                                        | 7  |  |  |  |  |

|   |      | 2.1.1 SCADE modelling language                                               | 7  |  |  |  |  |

|   |      | 2.1.2 SCADE Tool Suite                                                       | 8  |  |  |  |  |

|   |      | 2.1.3 Formal Verification using SCADE DV                                     | 9  |  |  |  |  |

|   | 2.2  | PROMELA/ SPIN                                                                | 10 |  |  |  |  |

|   | 2.3  |                                                                              |    |  |  |  |  |

|   | 2.4  | Satisfiability Modulo Theories                                               | 11 |  |  |  |  |

|   | 2.5  | LLVM                                                                         | 12 |  |  |  |  |

| 3 | GAI  | LS System-Level Validation                                                   | 13 |  |  |  |  |

|   | 3.1  | •                                                                            |    |  |  |  |  |

|   | 3.2  | * **                                                                         |    |  |  |  |  |

|   | 3.3  | Root Causes for Verification Threats                                         |    |  |  |  |  |

|   | 3.4  |                                                                              |    |  |  |  |  |

|   |      | 3.4.1 Detection of False Negatives                                           | 15 |  |  |  |  |

|   |      | 3.4.2 Detection of False Positives                                           | 16 |  |  |  |  |

|   |      | 3.4.3 Summary of Validation Obligations With Respect to Verification Results | 17 |  |  |  |  |

|   | 3.5  | Contract Validation                                                          | 17 |  |  |  |  |

|   |      | 3.5.1 Contract Insufficiencies                                               | 17 |  |  |  |  |

|   |      | 3.5.2 Contract Inconsistencies                                               | 17 |  |  |  |  |

|   |      | 3.5.3 Contract Weaknesses                                                    | 18 |  |  |  |  |

| 4 | Don  | nain Specific Contract Modeling Language for Users                           | 21 |  |  |  |  |

|   | 4.1  | Objectives                                                                   | 21 |  |  |  |  |

|   | 4.2  | Abstract Language Description                                                | 22 |  |  |  |  |

|   | 4.3  | Specifying and Exploiting Guaranteed Behavior                                | 23 |  |  |  |  |

|   |      | 4.3.1 Guaranteed Behavior in Contract Specifications                         | 23 |  |  |  |  |

|   |      | 4.3.2 Patterns of Guaranteed Behavior                                        | 24 |  |  |  |  |

|   | 4.4  | Realization with Enterprise Architect                                        | 25 |  |  |  |  |

|   | 4.5  | Rules for the CDSL $\rightarrow$ GTL Transformation                          | 28 |  |  |  |  |

| 5 | Text         | Textual Contract Specification Language GTL 29              |  |  |  |  |

|---|--------------|-------------------------------------------------------------|--|--|--|--|

|   | 5.1          | Syntax                                                      |  |  |  |  |

|   |              | 5.1.1 Expressions                                           |  |  |  |  |

|   | 5.2          | Grammar                                                     |  |  |  |  |

|   | 5.3          | Data types                                                  |  |  |  |  |

|   | 5.4          | Semantics                                                   |  |  |  |  |

|   |              | 5.4.1 Type system                                           |  |  |  |  |

|   |              | 5.4.2 Semantics of SCADE-components                         |  |  |  |  |

|   |              | 5.4.3 Semantics of GTL-components                           |  |  |  |  |

|   |              | 5.4.4 Semantics of GALS models                              |  |  |  |  |

|   | 5.5          | Restrictions of GTL specifications                          |  |  |  |  |

| 6 | This         | page has been left intentionally blank 43                   |  |  |  |  |

| 7 | Mod          | lel Transformations and GALS-Verification 45                |  |  |  |  |

|   | 7.1          | Transformation of component contracts to automata           |  |  |  |  |

|   | 7.2          | Transformation of Components to PROMELA processes           |  |  |  |  |

|   |              | 7.2.1 Native Integration                                    |  |  |  |  |

|   |              | 7.2.2 Contract abstraction                                  |  |  |  |  |

|   |              | 7.2.3 Verification goals                                    |  |  |  |  |

|   | 7.3          | Transformation of Components to UPPAAL timed automata       |  |  |  |  |

|   | 7.4          | Translation of Component Contracts to Synchronous Observers |  |  |  |  |

|   | 7.5          | Asynchronous Execution of processes                         |  |  |  |  |

|   |              | 7.5.1 Full asynchronicity                                   |  |  |  |  |

|   |              | 7.5.2 Synchronicity with non-determinism                    |  |  |  |  |

|   |              | 7.5.3 Bounded asynchronicity                                |  |  |  |  |

|   |              | 7.5.4 Synchronicity w.r.t. global dense time                |  |  |  |  |

|   | 7.6          | Transformation to an SMT instance                           |  |  |  |  |

|   |              | 7.6.1 Verification goal encoding                            |  |  |  |  |

|   |              | 7.6.2 Encoding of timed properties                          |  |  |  |  |

|   | 7.7          | LLVM verification of contracts                              |  |  |  |  |

| • | <b>T</b> 7 • |                                                             |  |  |  |  |

| 8 |              | fication of GALS models 59                                  |  |  |  |  |

|   | 8.1          | Abstraction by contracts                                    |  |  |  |  |

|   | 8.2          | Verification steps                                          |  |  |  |  |

|   | 8.3          | Refinement of contracts                                     |  |  |  |  |

| 9 | Bou          | nded Model Checking and Model-Based Testing 65              |  |  |  |  |

|   | 9.1          | Model-Based Testing                                         |  |  |  |  |

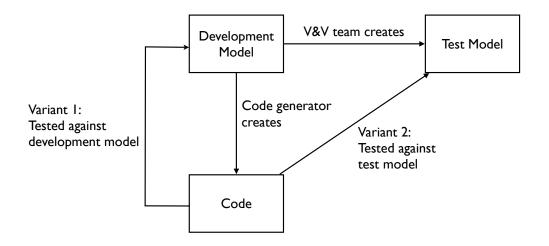

|   | 9.2          | Development Models Versus Test Models                       |  |  |  |  |

|   | 9.3          | Basic MBT Automation Techniques                             |  |  |  |  |

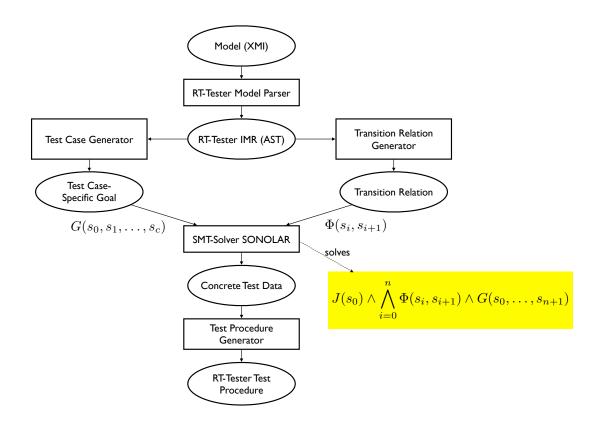

|   | 9.4          | Model-Based Test Case Generation                            |  |  |  |  |

|   | 9.5          | Computations, Traces and Model Coverage                     |  |  |  |  |

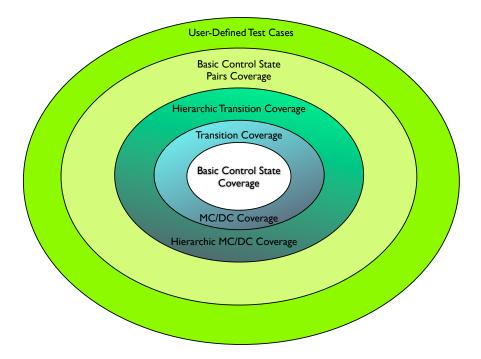

|   | 9.6          | Model Coverage Strategies                                   |  |  |  |  |

|   | 9.7          | User-Defined Test Cases                                     |  |  |  |  |

|   |              | 9.7.1 SafetyLTL                                             |  |  |  |  |

|   |              | 9.7.2 Encoding SafetyLTL Formulas as BMC Instances          |  |  |  |  |

|    | 9.8  | Bounded Model Checking of LTL Properties                                          |  |  |  |  |

|----|------|-----------------------------------------------------------------------------------|--|--|--|--|

| 10 | Equi | ivalence Class Testing 79                                                         |  |  |  |  |

|    | 10.1 | Introduction                                                                      |  |  |  |  |

|    | 10.2 | Reactive Kripke Structures                                                        |  |  |  |  |

|    |      | 10.2.1 Notation and Definitions                                                   |  |  |  |  |

|    |      | 10.2.2 Quiescent Reduction                                                        |  |  |  |  |

|    |      | 10.2.3 Traces                                                                     |  |  |  |  |

|    |      | 10.2.4 Input Traces                                                               |  |  |  |  |

|    |      | 10.2.5 I/O Equivalence                                                            |  |  |  |  |

|    | 10.3 | Input Equivalence Class Partitionings Over Reactive Kripke Structures With Finite |  |  |  |  |

|    |      | Outputs                                                                           |  |  |  |  |

|    | 10.4 | Test Hypotheses and Proof of Exhaustiveness                                       |  |  |  |  |

|    | 10.5 | Test Strategy                                                                     |  |  |  |  |

|    |      | 10.5.1 Complexity Considerations                                                  |  |  |  |  |

|    | 10.6 | Related Work                                                                      |  |  |  |  |

|    |      | Conclusion and Future Work                                                        |  |  |  |  |

|    |      |                                                                                   |  |  |  |  |

| 11 | Stoc | hastic Model Checking 93                                                          |  |  |  |  |

|    | 11.1 | Introduction                                                                      |  |  |  |  |

|    |      | 11.1.1 Background: Safety Versus Reliability in Communicating Railway Control     |  |  |  |  |

|    |      | Systems                                                                           |  |  |  |  |

|    |      | 11.1.2 Objectives and Contributions                                               |  |  |  |  |

|    |      | 11.1.3 Related Work                                                               |  |  |  |  |

|    |      | 11.1.4 Overview                                                                   |  |  |  |  |

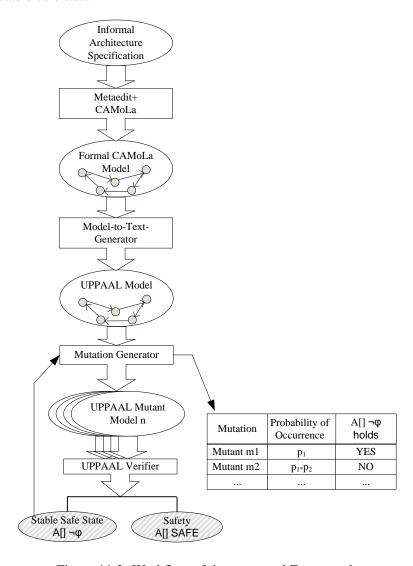

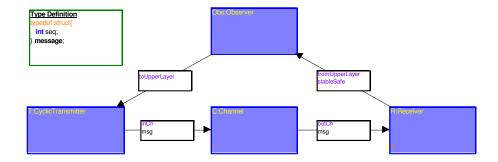

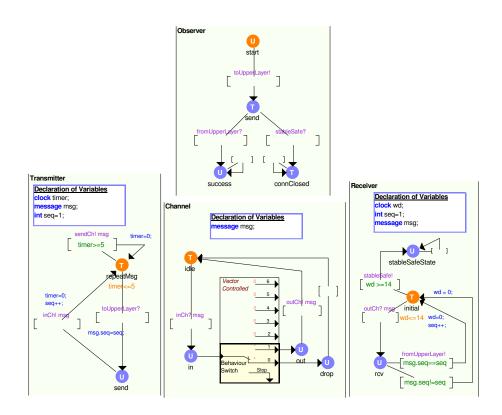

|    | 11.2 | orkflow and Tool Chain                                                            |  |  |  |  |

|    | 11.3 | The Communication Architecture Modelling Language CAMoLa                          |  |  |  |  |

|    |      | Mutation Generation and Reliability Calculation                                   |  |  |  |  |

|    |      | Discussion and Future Work                                                        |  |  |  |  |

|    |      |                                                                                   |  |  |  |  |

| 12 | Case | Studies 10:                                                                       |  |  |  |  |

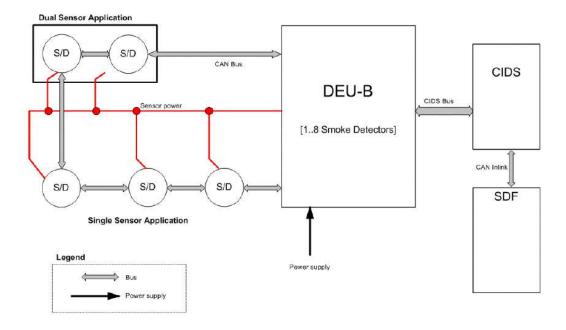

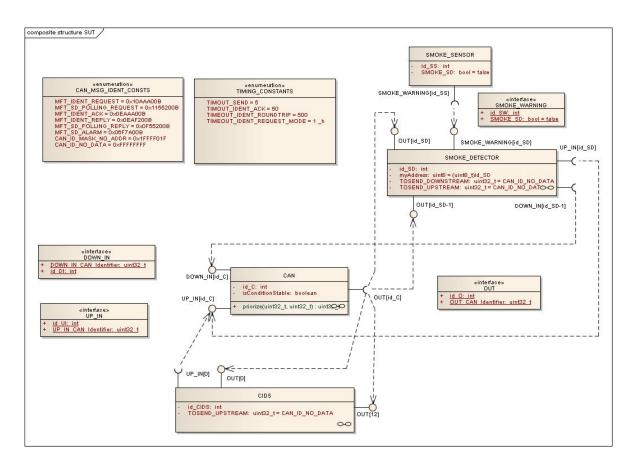

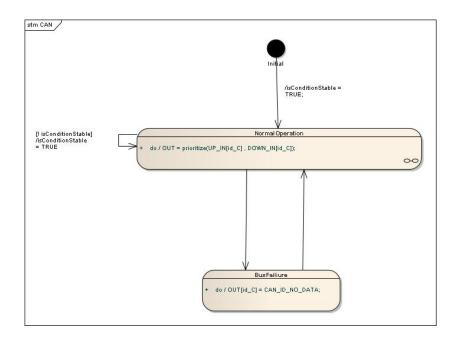

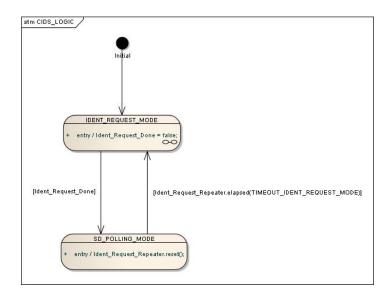

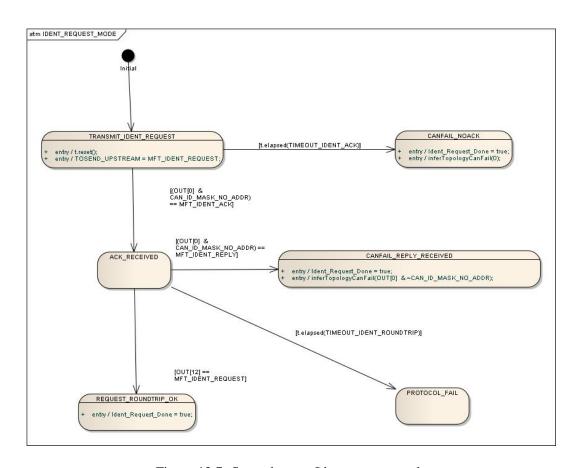

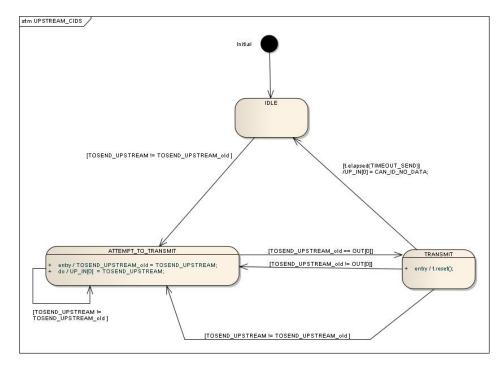

|    | 12.1 | Cabin Smoke Detection in Airplanes                                                |  |  |  |  |

|    |      | 12.1.1 Goals of the Smoke Detection Case Study                                    |  |  |  |  |

|    |      | 12.1.2 The A350xwb Smoke Detection Protocol                                       |  |  |  |  |

|    |      | 12.1.3 Analysis of the Smoke Detection Model                                      |  |  |  |  |

|    |      | 12.1.4 Assessment of Results                                                      |  |  |  |  |

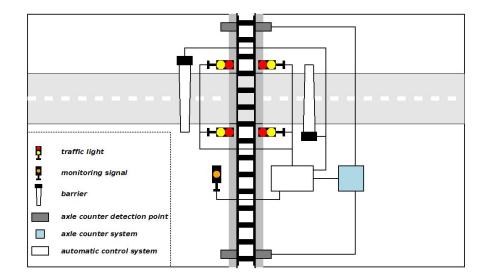

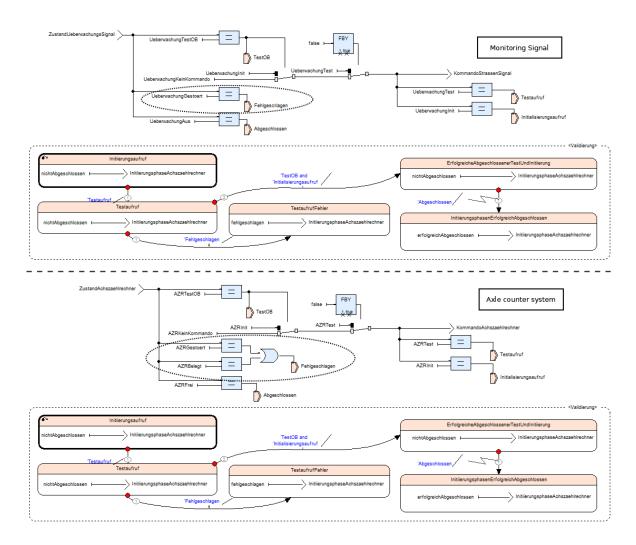

|    | 12.2 | Level Crossing Systems                                                            |  |  |  |  |

|    |      | 12.2.1 Requirements                                                               |  |  |  |  |

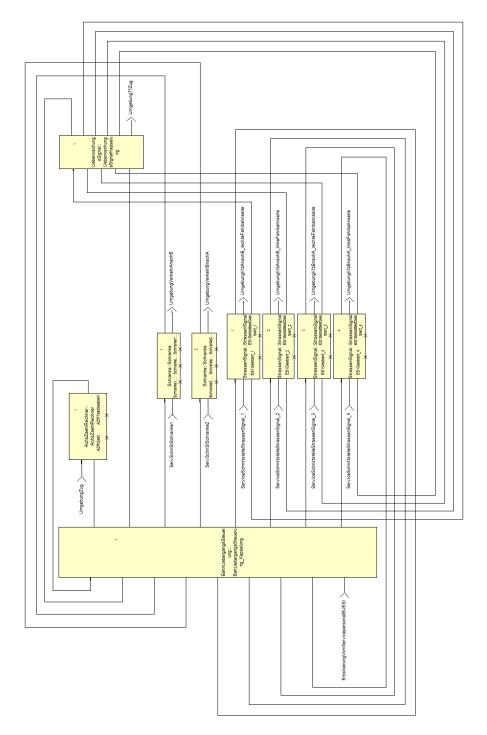

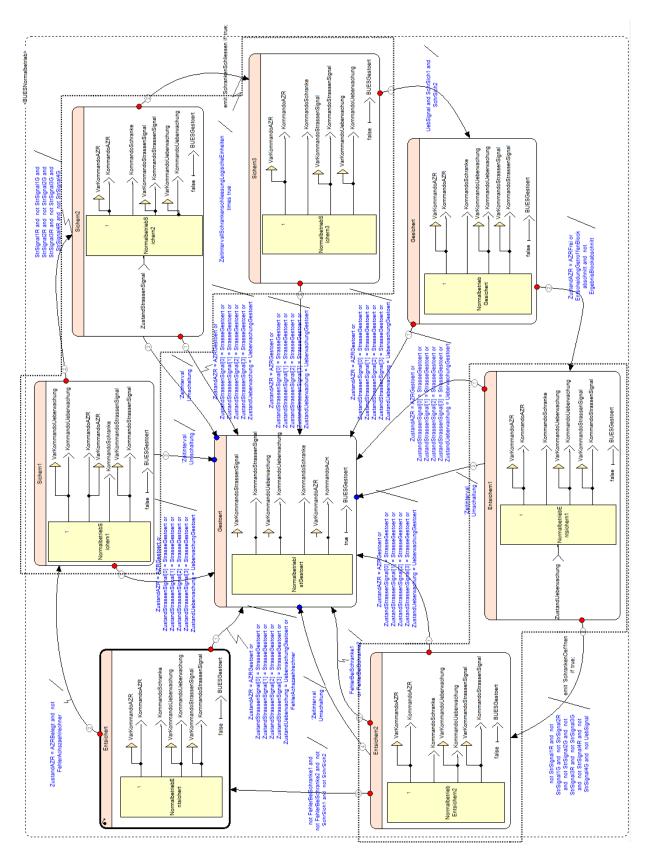

|    |      | 12.2.2 System architecture                                                        |  |  |  |  |

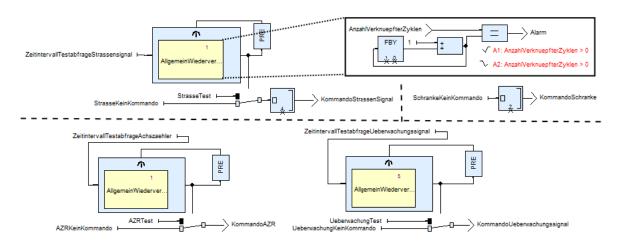

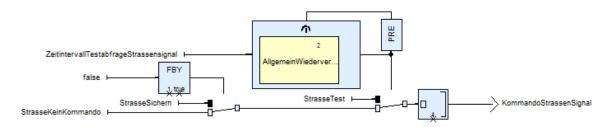

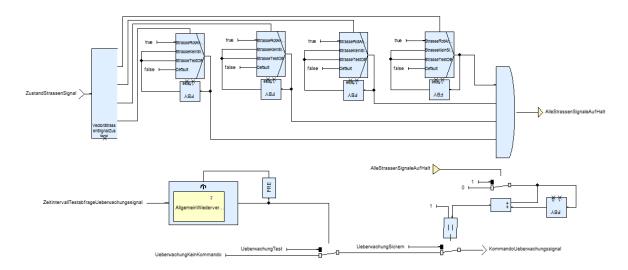

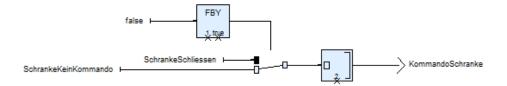

|    |      | 12.2.3 SCADE Models of System Components                                          |  |  |  |  |

|    |      | 12.2.4 Model-checking GALS Systems on the Source Code Level                       |  |  |  |  |

|    | 12.3 | Turn indicator                                                                    |  |  |  |  |

|    |      | Engine Start Stan Automatic                                                       |  |  |  |  |

| 13 | Validation of developed methods and comparison of model checking methods |     |  |  |

|----|--------------------------------------------------------------------------|-----|--|--|

|    | 13.1 CDLS Descriptions of Level Crossing Case Study                      | 155 |  |  |

|    | 13.2 Contracts and Verification of the Level Crosssing System            | 155 |  |  |

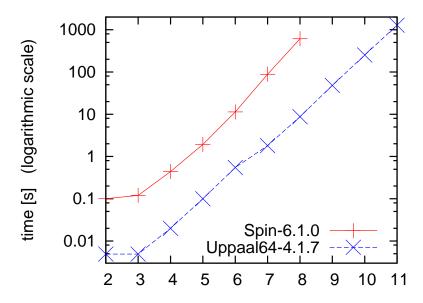

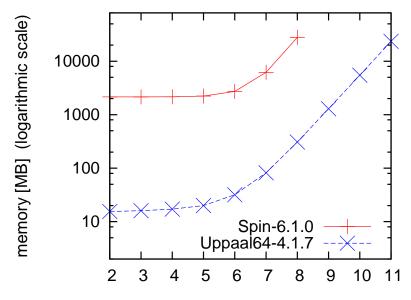

|    | 13.3 Benchmark of SPIN and UPPAAL Targets                                |     |  |  |

|    | 13.3.1 The Benchmark Example: Client-Server Mutex                        | 155 |  |  |

|    | 13.3.2 Generation of Input Data                                          | 157 |  |  |

|    | 13.3.3 The Measurement Process                                           | 158 |  |  |

|    | 13.3.4 Evaluation and Conclusion                                         | 164 |  |  |

|    | 13.4 Model Based Testing                                                 | 165 |  |  |

| 14 | Lessons Learned and Summary                                              |     |  |  |

| 15 | Summary and Future Work                                                  | 169 |  |  |

|    | 15.1 Further work                                                        | 169 |  |  |

| A  | Manual Smoke Detection Model in GTL (2 Smoke Sensors) - Full Listing     | 177 |  |  |

|    | A.1 Part that triggers large PROMELA output                              | 187 |  |  |

|    | A.2 Modified part with small PROMELA output                              |     |  |  |

| В  | Abbreviations used in the Smoke Detection Case Study                     | 191 |  |  |

| C  | C Appendix                                                               |     |  |  |

# **Chapter 1**

## Introduction

## 1.1 Problem description and main goals

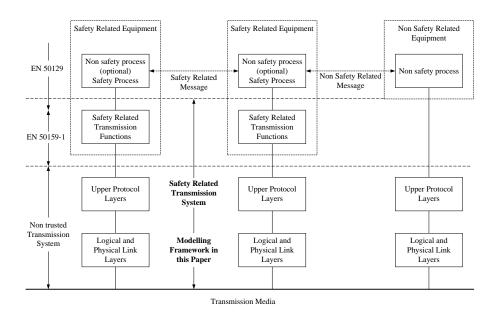

Computer systems are pervasive in everyday life and often carry responsibility for human lifes, e. g. in airplane autopilots or train control systems for railways. Such safety-critical systems must thus adhere to very high quality requirements concerning safety, reliability and availability. Hence, a very high effort has to be put into verification, validation and certification. The necessary measures to ensure the required high quality of the software of safety critical system are regulated through standards (e.g. CENELEC EN 50128 for the railway domain, DO178B for the avionics domain, as well as IEC 26262 for the automotive domain) that must be adhered to during the development process. The use of **formal methods** in the software development process is highly recommended by the standards. They allow to model and verify important and safety relevant logical functionality of a software at an early point during the development process and independently from hardware platforms used later on for deployment of systems. It is important to notice here that state-of-the-art systems are almost always composed from other distributed (component) systems (**system-of-systems** (**SoS**)). This is, however, still a challenge for formal methods when scalability to real industrial applications is regarded.

The goal of VerSyKo is the development of a general and universal approach to modeling and verification of software of distributed safety critical embedded systems; an approach that is innovative for the industrial practice and adresses the scalibility problem. The project focuses on the model based development and analysis of asynchronously communicating embedded control systems that are composed from components that operate synchronously. This system paradigm is known as GALS (globally asynchronous-locally synchronous) architecture. For complex safety relevant control tasks this is the most preferred solution: in the nodes of the distributed system one has controllers performing specialized tasks in hard real time by operating cyclically and in a synchronous way. For such a controller the model based development approach of SCADE is an attractive solution, which provides code generation, (formal) verification and test automation. Today, the relevance of the synchronous paradigm has been widely acknowledged in the scientific communities. Moreover, attractive alternatives to SCADE – such as synchronous interpretations of UML2 or Matlab/Simulink models – are also available, reducing the risk for industry to invest into this paradigm, which represents a new technology according to the state of the art in many companies.

However, for a whole distributed system, a synchronous implementation is neither realistic from a technical point of view nor desirable from the point of view of applications. Instead, locally synchronous nodes are integrated through a surrounding layer of software (often called *glue code*) that provides the necessary infrastructure for asynchronous communication. As a result, the SCADE (or

any other purely synchronous) formalism cannot be applied to a system of systems. Within VerSyKo we will close this methodological gap between synchronous component systems and asynchronous system of systems through domain specific modeling formalisms. The main emphasis is upon modeling and specification (with and without explicit consideration of real time and stochastic aspects pertaining random component failures), verification, validation and test. Domain specific formalisms are developed as UML 2.x profiles. They incorporate graphical representations and user friendly syntax for specification of GALS systems tailored towards system engineers with background in the respective application domain.

The main idea to address the complexity issues of GALS system is to provide for each synchronous component an abstract model in the form of a **contract** that can be locally verified for the component (e. g., for components modeled in the SCADE formalism by the formal verification engine provided by SCADE). The network of all component contracts then forms an **abstract GALS model** against which a requirement can be formally verified.

Another goal of the project is to provide tools for effective system testing: in an SoS scenario, local components of the GALS system network will have been thoroughly tested and even formally verified before their integration into the SoS network. These local verification results are denoted by **guaranteed behavior** of the associated local synchronous components. In the current approach to SoS testing applied in practice today it has to be criticised that the resulting tests frequently just "redo" variants of the HW/SW integration tests already performed by component suppliers, so that the system-level tests fail to increase the confidence into overall system correctness and effectiveness. It is therefore an explicit goal of this project to elaborate a systematic strategy for exploiting guaranteed behavior in the design of system verification goals and test strategies: documented proven behavior helps to avoid duplication of HW/SW integration tests on system level, and at the same time serves as counter examples or as means to strengthen contracts during the abstract GALS model verification process.

To evaluate all methods, languages and tools developed by VerSyKo we will use two case studies provided by the industrial partners; one case study from the railway domain and one from the avionics domain.

## 1.2 Overview of main concepts/tools developed by VerSyKo

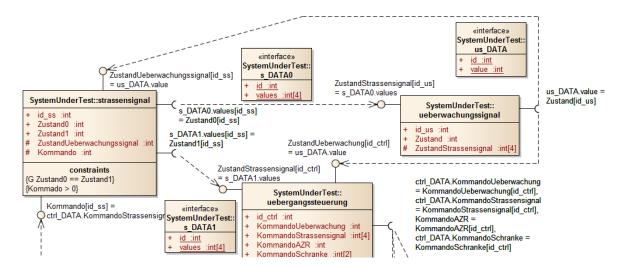

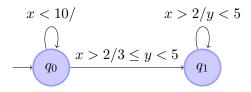

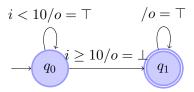

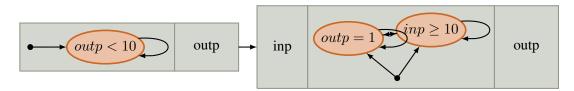

The goal is VerSyKo is to develop a framework for specification and verification of GALS systems. This specification framework is described in Sections 4 and 5. It allows to specify the synchronous components of a system and how they are composed to form the whole system. For each synchronous component an interface with its input and output data is specified. Components are composed by connecting their outputs with inputs of other components. To each component its implementation in a synchronous language (e. g. SCADE) is associated. In order to make verification possible the behavior of each component is described by one or more *contracts*. Each contract is either specified as a formula in linear temporal logic or by a synchronous state machine. Contracts are thought as an abstraction of the complete behavior of a concrete component, the latter of which is given by its associated SCADE model. So a GALS systems is specified as a "network of contracts" in our framework called *abstract GALS model*.

There is a special form of contract called a *guaranteed behavior*. Such a contract specifies behavior of a component that the corresponding SCADE model is known to fulfil. This could be behavior verified by testing or formal verification by the supplier of a component before integration into the GALS system.

Our specification formalism supports multiple instances of components. This is necessary because GALS systems often contain many instances of certain—possibly very simple—components (see for example our avionics case study in Section 12.1).

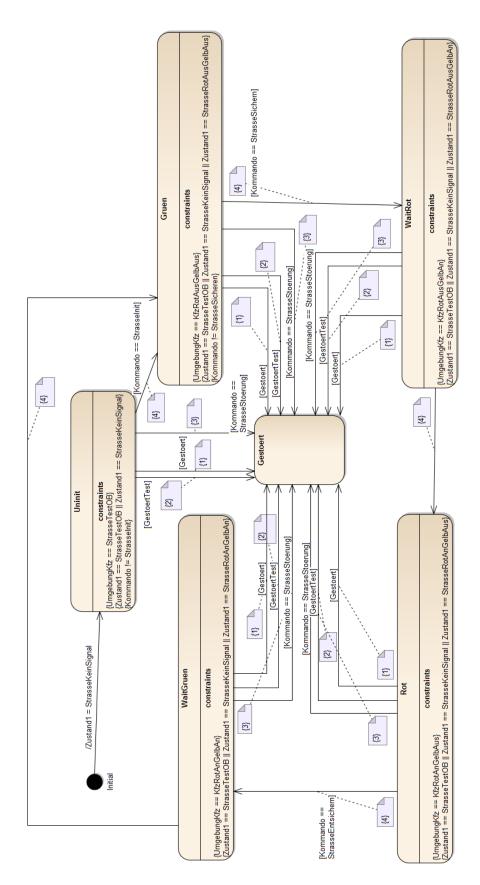

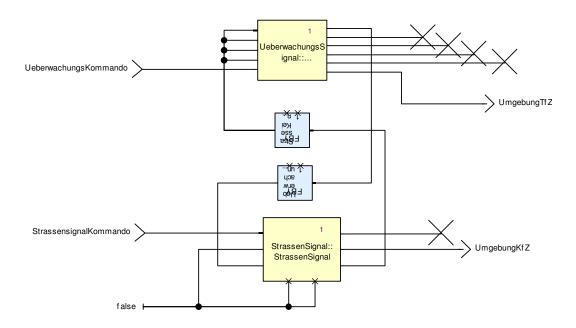

In addition to the components (their instances) and the connections between them one also specifies *verification goals*. They express system requirements (in the form of safety properties) that the integrated GALS system has to satisfy. While for a single synchronous component linear temporal logic and synchronous automata are sufficient, on the global level one needs to be able to formulate properties that refer to real time, and so on the global level we have a dense time semantics. Whenever verification goals do not refer to real time formal verification can be performed with an analysis tool based on a interleaving semantics (PROMELA/SPIN). Otherwise a real time formalism liked UPPAAL timed automata is necessary.

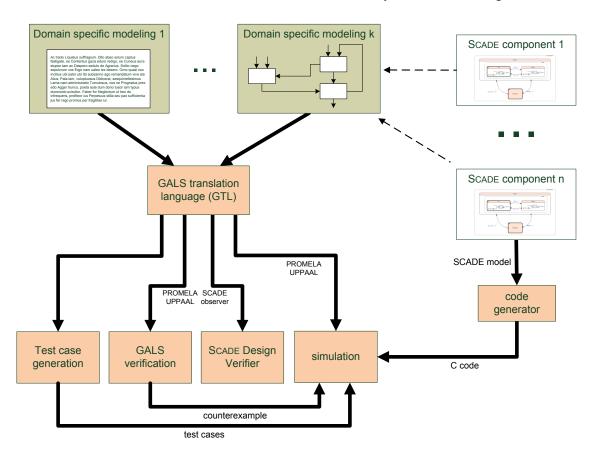

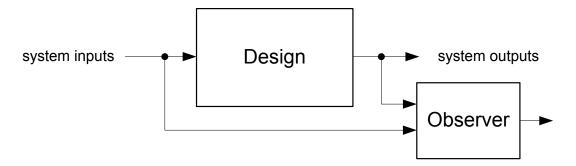

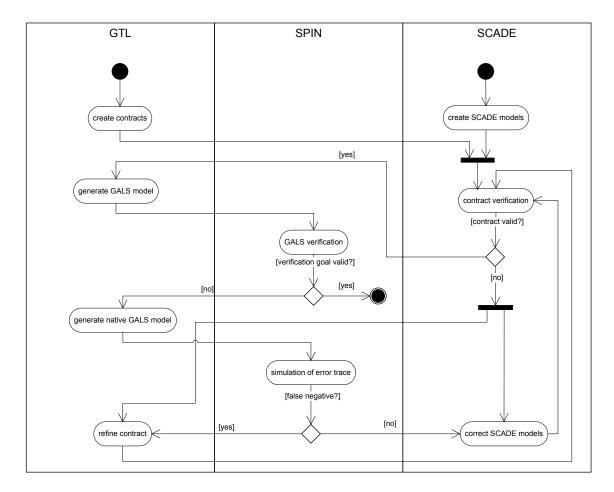

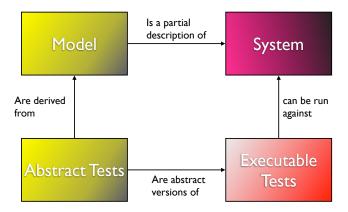

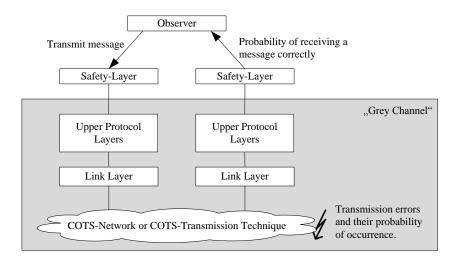

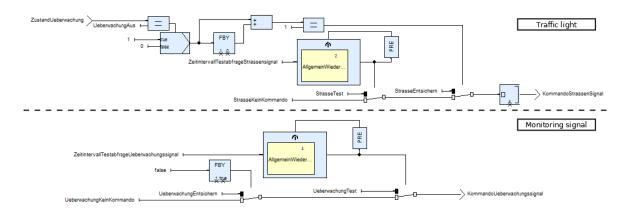

The overall architecture of the framework consists of three layers as shown in Fig. 1.1.

Figure 1.1: Framework for verification, validation and test of GALS systems

The top layer is a domain specific modeling language to specify GALS systems. This layer uses a mixture of graphics and text for specification. It is based on a UML profile and prototypical tool support is developed in Enterprise Architect<sup>1</sup>. This is described in detail in Section 4.

On the middle layer we have a textual form of the specification of a GALS system. For this VerSyKo develops a specification language for GALS systems called *GALS Translation Language* (GTL). Its purpose is to have a stable language core so that (1) on top of it one can build extensions

<sup>&</sup>lt;sup>1</sup>Enterprise Architect is an UML case tool developed by Sparx Systems http://www.sparxsystems.com.

and user friendly graphical respresentations like the one we develop on the first level and (2) various model transformations to test automation and formal verification formalisms and tools can be defined. We describe the syntax and semantics of GTL in Section 5.

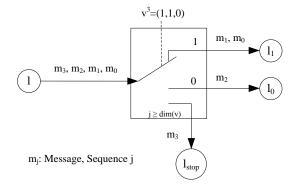

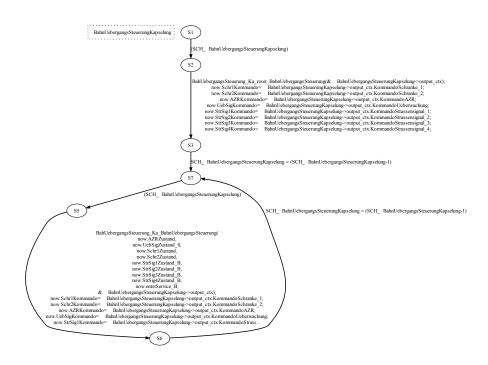

From the GTL level there are four kinds of model transformations considered in VerSyKo. We briefly describe them here; the corresponding details and algorithms are described in Section 7.

The purpose of the first transformation is local verification of components, i. e., the formal verification that components (given by their SCADE models) satisfy their contracts. So this transformation translates the contracts of each component into a synchronous observer for the component, and uses the SCADE Design Verifier (DV) (the formal verification component of SCADE) to prove that components satisfy their contracts. This transformation ignores any guaranteed behaviors of a component as those are already known to hold for the components. SCADE DV has limitations because its proof engine is based on a SAT solver and because it uses the SCADE syntax to specify properties for formal verification. So there is only a fragment of the GTL language that can be translated. Within VerSyKo we also plan to use *bounded model checking* for this kind of local verification. Here a model transformation that takes a SCADE model of a component and the contracts of the component and produces input for a bounded model checker will be implemented.

The second kind of transformation is for the verification of GALS systems. So the purpose is to verify the verification goals for a GALS system. This transformation translates the abstract GALS model ("network of contracts") to an appropriate analysis tool to perform this formal verification. Within VerSyKo we will develop two such model transformations. One uses PROMELA/SPIN as backend for formal verification, and this allows to verify verification goals that do not refer to real time. The second one uses UPPAAL timed automata as backend and this allows the verification of real time properties. Once these transformations are implemented in prototypical form we will also investigate how well the two different verification backends perform.

It is interesting to note that the guaranteed behaviors also play a special rôle for this GALS verification. In a first verification attempt they may not be translated to the verification backend. Instead they can be used for automatic abstraction refinement in the case of "false negatives" as explained next in connection with the third model transformation.

The third model transformation makes use of the C integration in SPIN. Its main purpose is to eleminate "false negatives" within the verification results. False negatives are spurious counterexamples produced by a verification backend to show that a verification goal does not hold for the abstract GALS model while it is actually true for the corresponding concrete GALS model ("network of implementations"). For the SPIN verification backend we can make use of the C integration in PROMELA to recognize false negatives. This works as follows: suppose we are given an error trace from the formal verification of a verification goal. Then our third model transformation integrates the C code generated from all SCADE models for the components of a GALS system into one PROMELA model. Now one simulates this model with the given error trace to see whether the simulation indeed exhibits erroneous behavior. If not then one has found a false negative, which is an indication that the contracts of the components were not strong enough to force the verification goal. In this case one can use guaranteed behaviors to strenthen the contracts. This means that the formal verfication of the whole GALS system is rerun but this time taking into account one or several guaranteed behaviors as additional contracts. In addition one might also use the error trace produced by the previous verification for strengthening contracts, as it was verified by model simulation that this trace does in fact not occur with the SCADE implementations.

Finally, the fourth kind of transformation in Fig. 1.1 above is for test case generation. Here the abstract GALS model is understood as a test model for the integration test of the components. So a test case generator extracts test cases from this model which can then drive a test environment (e. g. the

above simulation model in PROMELA or RT-Tester<sup>2</sup>) in which the concrete GALS model is tested.

#### 1.3 Related Work

Numerous works are devoted to combining synchrony with asynchrony, or to extend synchronous modeling towards less synchronous applications (see e. g. [18] for a summary on work on synchronous languages).

The concept of a GALS system was first investigated by Chapiro [30]. The GALS paradigm has mainly been studied in connection with hardware systems (see e. g. [13, 19]). More recently, GALS is also investigated in connection with software systems. For example, the formal verification of GALS systems by a combination of synchronuous and asynchronuous formalisms appears in several different works:

- (1) Thivolle and Garavel [41] explain the basic idea and show the advantages of the GALS approach by applying it to the verification of a communication protocol. The paper explains how synchronous components can be understood as functions and how these components can be integrated into an asynchronous verification tool. In contrast to our work in VerSyKo this work does not develop a language for the specification of GALS systems, and components are not abstracted by contracts as in our work. The paper only treats one example where synchronous components are integrated into a GALS system.

- (2) Doucet et al. [38] describes a translation from the synchronous language SIGNAL to PROMELA. The verification of translated GALS models is then performed using SPIN. The idea to use contracts as abstractions of synchronous components and formally verify those contracts within the synchronous formalism is new in our work in VerSyKo.

- (3) "Communicating Reactive State Machines" [86] are another formalism for modelling and verification of GALS systems. The code is translated to PROMELA and verified using SPIN. The described system is comprised of a graphical editor, a simulator and a verification engine. Apart from the well researched method of slicing, no further optimization techniques are being discussed.

- (4) The "IF toolset" [25] introduces a formalism for the specification of asynchronous systems. This formalism is based on components and their composition by connections. That work does not focus on GALS systems but rather on a formalism that can integrate many different design formalisms.

We now mention three approaches to deal with asynchrony which are less related to the work in VerSyKo.

The first approach to dealing with asynchrony is to extend synchronous formalisms. For example, "Multiclock Esterel" [85] extend the Esterel synchronous language by a possibility to supply several clocks for different components. However, this formalism remains fully synchronous and every model can be translated into an equivalent Esterel model.

Secondly, a different line of research deals with compiling synchronous programs to produce distributed, not strictly synchronous code which is correct-by-construction. One example of this is [83].

<sup>&</sup>lt;sup>2</sup>RT-Tester is the real time test tool developed by Verified Systems

Thirdly, an approach we do not follow in VerSyKo is to use synchronous formalisms to model asynchrony. This idea goes back to R. Milner [73, 74]. The modeling tool Model-Build [15, 16] and the Polychrony workbench [68] are based on this idea and also the work in [54, 63, 76].

It is well-known that formal verification of synchronous (component) programs, in particular SCADE models, can be performed by using synchronous observers to specify properties (see [53, 55]). An application of this approach in an industrial context is for example [36]. Further work on formal verification of SCADE models concerns formal safety analysis (see [2] and [50]). We are not aware of work that uses abstraction of components in connection with formal verification in SCADE.

The concept of systems of systems (i. e., systems being composed of components) also appears in numerous works. For example, one formal model of a system component are interface automata [6]. While this formalism deals well with composition and refinement the components have asynchronous behavior in contrast to what we study in VerSyKo.

Using contracts as specifications for parts of a program or system is also not a new idea; see for example work on rely/guarantee logic [64]. The idea to abstract systems components by contracts appears recently for example in [45, 44]. The specification language used there is based on UML and the work does not deal with synchronous components and GALS systems.

So the various ingredients (contracts for abstraction, synchronous verification, GALS systems) of our work are well-established in the literature. However, to the best of our knowledge these ingredients have not been brought together in one single practical framework. It is this gap that we intend to fill with VerSyKo.

# Chapter 2

# **Prerequisites**

In this section we recall those concepts, languages and tools that form the background for the work in VerSyKo that we present in the subsequent sections.

#### 2.1 SCADE

The SCADE tool suite (Safety-Critical Application Development Environment) is a model-based development framework for safety-critical software. It supports certification of systems according to common standards from the aviation and rail transportation industries.

#### 2.1.1 SCADE modelling language

The SCADE modeling language is a synchronous and dataflow-oriented language based on LUSTRE [52], and was extended by safe state machines [9]. The SCADE semantics is based on the "synchronous hypothesis" which states that the calculation of a model's clock cycle does not consume any time. Of course, this assumption is a simplification and cannot be fulfilled by real systems. Nevertheless, all logical operations and causal interrelations may be modelled. For the practical use, the simplifying assumption only implies the following restriction: The calculation time used by the model within one cycle must be smaller than the cycle time allocated to one clock cycle. The SCADE language is deterministic and there are no run-time effects. Each language construct has a graphical representation in the editor of the tool suite. An brief overview of the language constructs follows below (for further details see the SCADE tutorial and language reference):

**Data:** SCADE permits the handling of structured data. All data structures are static. It is possible to build structures and arrays from the basic types (real, int, bool). The modeling language is strongly typed.

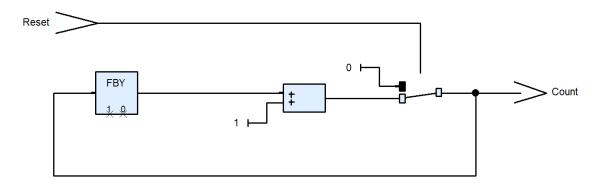

**Data-flow modeling:** The SCADE modelling language includes the usual Boolean logic (and, or, not etc.) and arithmetic (+, -, \*, etc.) operators to form expressions on dataflows. A conditional operator (if-then-else) allows to switch between two dataflows according to the value of a Boolean dataflow. In addition, the temporal operator fby ("followed by") allows to access data flow values of past clock cycles. There are operators for accessing structures and arrays including a dynamically indexed array access. However, there is no way of explicitly describing loops. Instead there are the "algebraic loops" Map and Fold, which are well-known in functional programming. Map is used to apply an operator with a certain input data type to an array of that data type element-wise. With Fold, calculations may be accumulated over an array. Fig. 2.1 shows an example of a simple SCADE model.

Figure 2.1: SCADE model of a simple counter

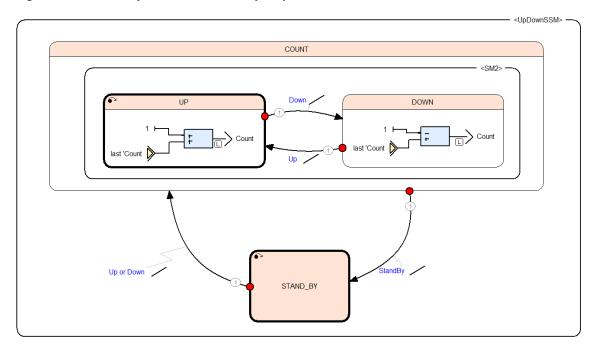

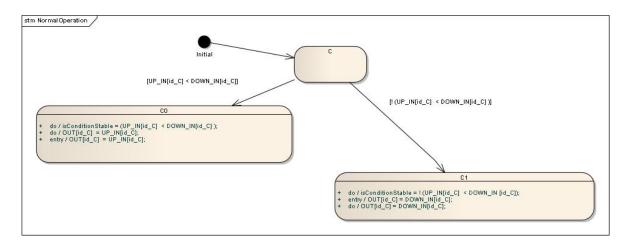

**State machines:** The state machines in SCADE are synchronously clocked, hierarchic state machines, so called safe state machines [9].

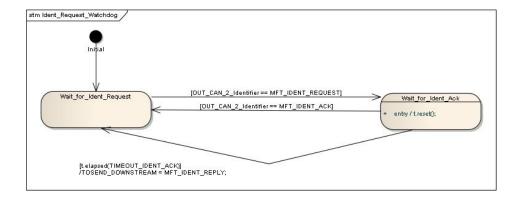

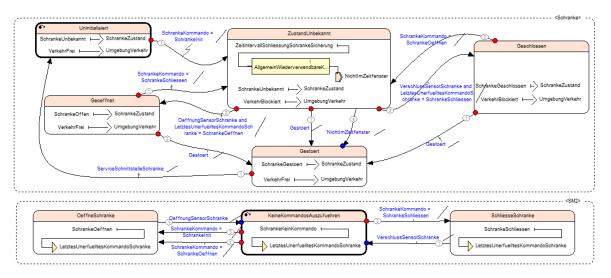

They look similar to UML state charts. However, an important difference is the strictly synchronous semantics: In each clock-cycle and in each (parallel) state machine precisely one state and precisely one transition is active and being carried out. Cyclical dependencies between model elements are not permitted and are, at code generation time, treated like syntax errors. Fig. 2.2 illustrates an example of a state machine. The two means of description, data flow and state machines, are fully integrated and thus may be combined in any way.

Figure 2.2: A state machine in SCADE

#### 2.1.2 SCADE Tool Suite

The SCADE suite provides extensive tool support for the SCADE modelling language. We list the main features:

**Graphical Editor:** As already mentioned, each syntactic model element has a graphical representation. In the SCADE editor, these graphical elements can be used for modelling. Also, a textual modelling language may be used.

**Code Generator:** The code generator creates a C code from SCADE models. This code generator is qualified for the development of safety-related software in accordance with the standards DO-178B [37], up to Level A, and with CENELEC EN 50128 [27], up to SIL 3/4.

**Simulator/Debugger:** This feature allows running the code generated from a SCADE model, to test it on the model level and to debug it. The simulator may be controlled via TCL scripts and provides an automation interface.

**Model Test Coverage:** This tool component allows measuring the structural coverage of a given model by a test suite. SCADE models may automatically be instrumented for measurements according to two different coverage criteria: Decision Coverage (DC) and Modified Condition/Decision Coverage (MC/DC). Other criteria may be easily supplied by the user for (self-modelled) libraries.

**Design Verifier (SCADE DV):** This tool component allows the formal verification of safety properties of SCADE models. As this feature plays an important role for VerSyKo we will describe it a bit more detailed in the next subsection.

**Gateways to other tools:** The SCADE suite provides a number of gateways to exchange data with other tools. The requirements gateway permits the linking of SCADE model elements with their requirements which are, for instance, recorded in a tool such as DOORS. Also, classically coded parts of the software and test cases may be linked.

Other gateways link the SCADE suite with Rhapsody, Simulink and ARTiSAN.

#### 2.1.3 Formal Verification using SCADE DV

The behavior of a SCADE design model can be given as a transition system  $\mathcal{T} = \langle S, I, \rightarrow \rangle$ , where S is a set of states,  $I \subseteq S$  is a set of initial states and  $\rightarrow \subseteq S \times S$  is the transition relation, see [2]. For efficiency reasons, the SCADE DV transforms a design model into a set of Boolean and linear arithmetic formulas that symbolically represent  $\mathcal{T}$ . If P denotes a state predicate, i.e.  $s \models P \Leftrightarrow s \in P$ , SAT-based model checking enables to verify safety properties S:

$$\forall s_0, s_1, \dots s_n \in S : I \ni s_0 \to s_1 \to \dots \to s_n \Rightarrow s_n \in P.$$

In contrast to other approaches, the SCADE DV does not offer a temporal logic but properties have to be modeled as *synchronous observers* using the same language operators as for the design. This is illustrated in Fig. 2.3.

The synchronous observer is simply a SCADE operator having as input the inputs and outputs of the SCADE design to be verified and as output a Boolean data-flow. SCADE DV then verifies that this output is always true (i.e., the constant Boolean flow with value true). To perform formal verification SCADE DV uses the SAT based proof engine of Prover Technologies (http://www.prover.com). Notice, however, that more general temporal properties, notably unbounded liveness properties, cannot be automatically verified using this SAT-based approach.

<sup>&</sup>lt;sup>1</sup>Safety properties express that the system always stays in a good or "safe" state.

Figure 2.3: A state machine in SCADE

#### 2.2 PROMELA/SPIN

SPIN is a general tool for verifying the correctness of distributed software models in a rigorous and mostly automated fashion. It was written by Gerard J. Holzmann and others in the original Unix group of the Computing Sciences Research Center at Bell Labs, beginning in 1980. SPIN stands for *Simple* PROMELA *Interpreter*.

Systems to be verified are described in PROMELA (**Process / Protocol Meta Language**), which supports modeling of asynchronous distributed algorithms as non-deterministic automata [59]. Properties to be verified are expressed as Linear Temporal Logic (LTL) formulas, which are negated and then converted into Büchi automata as part of the model-checking algorithm. SPIN supports the verification of *safety* properties ("Something bad will never happen") as well as *liveness* properties ("Something good will eventually happen").

The SPIN tool uses an "explicit-state model checking" algorithm, i.e. it explores every reachable state of a system to verify whether the properties to be verified hold or not. If a property does not hold, then a counter-example in form of an execution trace leading to the illegal state is generated. In addition to model-checking, SPIN can also operate as a simulator, following one possible execution path through the system and presenting the resulting execution trace to the user.

SPIN also offers a large number of options to further optimize the model-checking process for speed and memory, such as:

- partial order reduction [47];

- state compression [58];

- bistate hashing (instead of storing whole states, only their hash code is remembered in a bitfield; this saves a lot of memory but voids completeness);

- · weak fairness enforcement;

- use of slicing-techniques to allow distributed model-checking on multi-processor systems [60].

Unlike many model-checkers, SPIN does not actually perform model-checking itself, but instead generates C sources for a problem-specific model checker. This technique saves memory and improves performance, while also allowing the direct insertion of chunks of C code into the model.

#### 2.3 Timed Automata and UPPAAL

UPPAAL is a model checking tool for dense real-time, developed jointly by UPPsala and AALborg university groups. First conceived in 1995, it has undergone a large number of optimizations and benchmark analyzes to make it applicable to a larger set of problems. Today it is widely used for educational purposes and has a sound reputation in industrial application.

The UPPAAL tool features a graphical editor, a simulator, and a verifier component. The verifier allows several user configurations on state space exploration, where the optimal configuration usually depends heavily on the system under investigation. Verification results can be used as input to the simulator, which allows to trace and explore unexpected model behavior.

The modeling language is an extension of the *timed automaton* formalism by Alur et al. [8]. UP-PAAL supports parallel operation of several state machines, that can synchronize on global variables, synchronization channels (hand-shake), or time. States can be equipped with (downward closed) invariants on clock variables. Additional annotations – like urgent or committed states or channel urgency – are powerful concepts to steer the timing behavior of a network of state machines and effectively reduce the size of the state-space to be explored. In the recent years more and more C-style constructs were added to the model syntax, including arrays, structured data types, and user functions.

The logical language consists of a small subset of timed CTL (TCTL) [8]. Untimed *local properties* are based on the automaton syntax, i.e. are Boolean expressions over variable values, automaton locations, and clock equations. Temporal properties are constructed from local properties by application of temporal operators (in a restricted way). The strongest construct is the *unbounded response*  $\phi$  -->  $\psi$ , which states that a state where local property  $\phi$  holds is always (eventually) followed by a state where local property  $\psi$  holds. The possibility of adding observer automatons allows to verify a wide range of interesting system properties.

While a large number of optimization techniques have found application in the UPPAAL tool, the most prominent ones might be the following:

- avoiding of expansion to the full symbolic state space (called *region graph* in [8]); rather use a compact representation, which includes efficient data types for clock relation representation

- restriction of supported verification formulas to a subset of verifiable properties, that still allow for efficient model checking algorithms

The success of the tool is at least partially owed to the careful selection of modeling language extension, which do not break these.

## 2.4 Satisfiability Modulo Theories

The *Satisfiability Modulo Theories* (or *SMT* for short) problem is a decision problem for formulas which extend first-order logic with certain theories. Its instances are a generalization of the boolean satisfiability problem (called *SAT*), because every SAT problem is also a SMT problem. On a fundamental level, the SMT problem asks: "Given a formula  $\varphi$ , is there a valuation of the variables in  $\varphi$  such that  $\varphi$  becomes true?".

In recent years, computer programs (so called *solvers*) have become increasingly efficient in solving SMT problems. A proposed standard, to which many SMT solvers adhere, is called *SMTLib*[14]. It specifies a communication protocol based on LISP data-structures to formulate problems and receive answers from the solver. Not only can modern SMT solvers check the satisfiability of a given formula, they can also

- Provide a valuation for the variables of the formula which make the formula true.

- Extend or reduce the formula to facilitate incremental solving of problems.

- Declare new data types and functions which can then be used in formulas.

By using the SMTLib standard, application developers can make the SMT solver exchangeable and thus profit from the multitude of different SMT implementations currently existing.

#### **2.5** LLVM

*LLVM*, which once was an acronym for "Low Level Virtual Machine" (now it's the full name of the project), is a collection of modular and reusable compiler and toolchain technologies. In the context of VerSyKo, two components of the LLVM framework are relevant:

- 1. The LLVM *intermediate representation* ("IR") language is high-level assembler language. Unlike most assembler languages, it is platform-independent and uses a static single assignment ("SSA") form instead of a register-based notation.

- 2. Clang is a compiler which can be used to translate C- and C++-programs into the LLVM-IR.

# Chapter 3

# **GALS System-Level Validation**

## 3.1 System-Level Verification Approach

As indicated in the introduction the VerSyKo approach to system-level verification is as follows (further details are described in Section 8):

- The system-level verification goal  $\Phi$  is specified as a (timed) LTL formula expressing the desired behavior of the GALS system.

- The behavior of each synchronous component C in the GALS network is abstracted by its **contract**  $\Phi_C$  which is expressed by an LTL formula (or other modeling techniques which are equivalent to expressing such a formula).

- From the network of contracts an **abstract GALS model**  $M_G$  is derived. This consists of a network of concurrent components C', such that each C' shows the most non-deterministic behavior still satisfying  $\Phi_C$ .

- It is verified by means of property checking whether  $M_G$  satisfies  $\Phi$ . We say that a **verification** succeeds if property checking shows  $M_G \models \Phi$  and the **verification fails**, otherwise.

- As additional verification artifacts, local test and verification results obtained during component verification and validation (V&V, for short) are provided as **guaranteed behavior**  $\beta_C$  by component suppliers. Again,  $\beta_C$  may be expressed as an LTL formula.

### 3.2 Verification Threats

Recall that the objective of **validation** is to check whether the system is adequate for its intended purpose, while **verification** checks the consistency of development artifacts with a reference specification (which may also be a model). The validation verdict is based on the collection of verification results achieved, in combination with specific validation activities, such as tests or formal verifications investigating the effectiveness of the system's operation in its intended environment<sup>1</sup>.

From the point of view of GALS system validation the verification on system-level as investigated in this project poses three threats, which we call **verification threats (VTH)**. Potential root causes leading to these threats will be analyzed in the sections below.

<sup>&</sup>lt;sup>1</sup>These tests and verifications complement the ones already performed during verification.

- 1. VTH 1: The verification fails because the implemented GALS system network is inadequate for the system-level specification. This is the "normal" verification, failure analysis and correction cycle that should finally lead to an improved system implementation.

- 2. VTH 2: The verification fails though the implemented GALS system network is *adequate* for its purpose. This situation is called a **false negative**: a correct system is rejected due to a verification failure which should not have occurred.

- 3. VTH 3: The verification succeeds though the implemented GALS system network is *inadequate* for its purpose. This situation is called a **false positive**: if not detected by system validation, an inadequate implementation will be accepted and become operative.

#### 3.3 Root Causes for Verification Threats

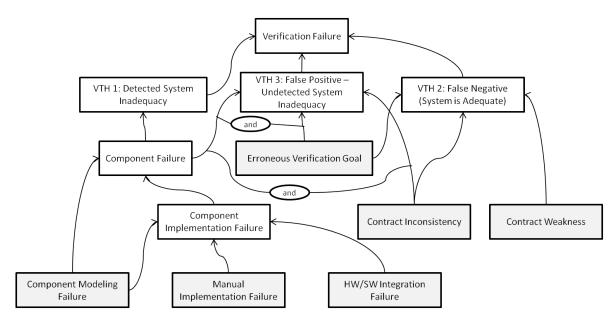

In Fig. 3.1 a root cause analysis for the verification threats introduced above is shown in the form of a cause-consequence graph. Each arrow  $A \to B$  in this figure has the meaning "A may cause B". The root causes are represented in Fig. 3.1 by the grey-shaded boxes possessing outgoing arrows only. Their meaning is defined as follows:

- Erroneous verification goal. The GALS system-level verification goal  $\Phi$  is inadequate for the ultimate goals of system validation, that is, the properties expressed by  $\Phi$  are not the ones required for the intended purpose of the system.

- Component modeling failure. A synchronous component has been modeled in a way that the implied behavior is not adequate for the GALS system.

- Manual implementation failure. The component (or some part of it) has been programmed in a manual way, and during this process a failure was injected into the implementation.

- **Contract inconsistency.** The contract describes a behavior which is inconsistent with the true behavior of the component.

- Contract weakness. The contract is consistent with the true component behavior, but asserts weaker properties than the ones actually fulfilled by the component.

- HW/SW integration failure. During HW/SW integration a failure is injected, such as faulty linkage of relocatable code, insufficient register word length for the occurring mathematical operations or firmware and microcode errors.

If VTH 1 applies, the GALS system-level verification fails due to a "real" failure of the system. This must have been caused by at least one erroneous component. The component's failure may either be reflected already in its model, or it may have been injected in a manual implementation step not captured by the model. Observe that in any case the component's contract must have captured the erroneous behavior, because otherwise the GALS system-level verification would not have failed.

A false negative (VTH 2) may have been caused by an erroneous GALS system-level verification goal, or by inadequate contracts. Both inconsistent or weak contracts may cause false negatives: in the former case the contract implies erroneous component behavior though the component will really perform in an adequate way; in the latter case the contract is consistent with the true component

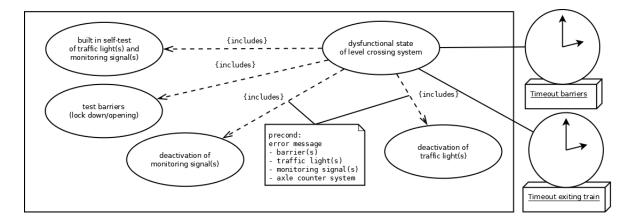

Figure 3.1: Root causes for verification threats.

behavior but too weak to prove the system-level verification goal. Typical variants of inadequate contracts will be discussed below.

Verification threat VTH 3 (false positive) applies in situations where at least one component is faulty but the system-level verification fails to detect this. This can be caused by an erroneous system-level verification goal or by a contract inconsistency which does not reflect a component's true faulty behavior. Observe that a contract weakness may never cause a false positive because it is always consistent with the true component behavior. Moreover, VTH 3 may be caused by a HW/SW integration failure which leads to component behavior which is even inconsistent with the software code.

### 3.4 Validation of System-Level Verification Results

From the perspective of system validation it is crucial to detect the presence of verification threats VTH 1, 2, 3 and abolish their causes. To this end, it has to be investigated first how to find out whether VTH 1, 2 or 3 are present in a verification result.

#### 3.4.1 Detection of False Negatives

Since both VTH 1 and VTH 2 lead to a system-level verification failure, it has to be decided after occurrence of this failure which of the two threats applies. The following techniques can be applied to identify false negatives. The negative model checking result on system level is associated with an **error trace**  $\pi = \langle s_0, s_1, s_2, \ldots, s_n \rangle$ , where each  $s_i$  is a valuation function mapping each interface symbol addressed in the abstract GALS model to its current value. Since  $\pi$  is a legal finite computation trace of the model  $M_G$  and  $M_G$  only consists of components C satisfying their contracts  $\Phi_C$ , computation  $\pi$  is consistent with each of these contracts,

$$\forall C : \pi \models \Phi_C.$$

Note that a contract  $\Phi_C$  may not necessarily address all interface variables of C in its LTL formula. We require, however, that the contract interface specification contains C's complete interface. As a consequence, each interface symbol x of C is in the domain of the valuation functions  $s_i$ , but the

model checker may have assigned a random value to  $s_i(x)$  if x is not further restricted by the LTL formula  $\Phi_C$ .

**False negatives caused by contract inconsistencies.** Now suppose that the false negative has been caused by a contract inconsistency. This can be uncovered in the following ways:

- If some component C is associated with a complete formal model  $M_C$  which is consistent with the true behavior of C, but C's contract  $\Phi_C$  is faulty, the inconsistency between  $\Phi_C$  and its model  $M_C$  can be simply uncovered by "local" model checking of contract  $\Phi_C$  against the model  $M_C$ , which will result in  $M_C \not\models \Phi_C$ .

- If no complete model  $M_C$  exists the guaranteed behavior  $\beta_C$  if provided by the supplier may be exploited: if  $\pi \not\models \beta_C$  then the error trace  $\pi$  is inconsistent with the assertions  $\beta_C$  already established, so  $\pi$  is not a trace of C. There can be two root causes for this inconsistency.

- 1. The contract  $\Phi_C$  is faulty.

- 2. A contract of another component  $C_0$  is faulty and  $C_0$  produces data consumed by C. The output data of  $C_0$  in  $\pi$  is consistent with the faulty contract  $\Phi_{C_0}$ , but violates the (correct) assumptions about admissible inputs in contract  $\Phi_C$ .

False negatives caused by contract weaknesses. Next assume that the false negative has been caused by a contract weakness of component C. This can be uncovered as follows:

- If a complete formal model  $M_C$  of C exists it can be shown that  $\pi$  is not a trace of this model,  $\pi \not\models M_C$ .

- If guaranteed behavior  $\beta_C$  is defined for C, the contract can be refined by  $\Phi_C \wedge \beta_C$  since the guaranteed behavior must be consistent with the contract. The refined contract may be harder to evaluate during model checking, but it may show that error trace  $\pi$  does not exist.

False negatives caused by erroneous system-level verification goals. If the false negative has been caused by an erroneous system-level verification goal  $\Phi$ , this can be identified by validating the error trace  $\pi$  and finding out that this trace should really be considered as legal, i.e.  $\pi$  is a correct trace of the system composed of components C.

#### 3.4.2 Detection of False Positives

Analyzing again the cause-consequence graph of Fig. 3.1 leading to false positives (VTH 3) yields the following case distinctions:

- If the false positive has been caused by contract inconsistencies while the system-level verification goal  $\Phi$  is adequate, it is again necessary to uncover this inconsistency. As explained above in the case of false negatives, this can be detected by checking  $\Phi_C$  against its model  $M_C$  and uncovering  $M_C \not\models \Phi_C$  or by proving that  $\Phi_C \land \beta_C$  has no solution.

- If the false positive has been caused by an inadequate system-level verification goal  $\Phi$  only guaranteed behavior in combination with simulations may help to uncover the failure situation: a system-level computation  $\pi$  fulfilling  $\Phi$  may contradict a guaranteed behavior  $\beta_C$  of some system component. Observe that C is not necessarily a component associated with a faulty

contract; the contradiction may have been caused by another component contributing to  $\pi$  in a way that violates the requirements of C.

#### 3.4.3 Summary of Validation Obligations With Respect to Verification Results

Summarizing, the following activities should be performed to validate system-level verification results:

• All contracts  $\Phi_C$  of components C associated with formal models  $M_C$  have to be checked with respect to validity of  $M_C \models \Phi_C$ .

This task can be performed by model checking.

• All components C associated with guaranteed behaviors  $\beta_C$  have to be checked with respect to consistency between contract and guaranteed behavior. This means to prove that solutions of  $\Phi_C \wedge \beta_C$  exist.

This task can be performed by SAT or SMT-solving, respectively.

- All error traces  $\pi$  rejected by the system-level verification goal  $\Phi$  have to be checked with respect to consistency with guaranteed behaviors,  $\pi \models \beta_C$ .

- All simulation traces  $\pi$  consistent with the system-level verification goal  $\Phi$  have to be checked with respect to consistency with guaranteed behaviors,  $\pi \models \beta_C$ .

#### 3.5 Contract Validation

#### 3.5.1 Contract Insufficiencies

As elaborated above, contracts of local components in the GALS network may be insufficient in two ways.

- Contracts may be **inconsistent** to their underlying detailed models.

- Contracts may be too weak to allow for the verification of the global GALS verification goal.

In any case an insufficient contract may lead to verification failures (**false negatives** or **false positives**) when trying to prove the global GALS verification goal.

In the sections below we classify typical patterns of inconsistencies and weakness that we know from practical experience to occur in contract specifications. We will then explain how each of these insufficiencies can be uncovered, exploiting local and global model checking techniques as well as the guaranteed behavior assertions available in contract specifications.

A frequently occurring pattern for contracts represented by LTL formulas is

$$\mathbf{G}(\phi \Rightarrow \psi)$$

(Whenever  $\phi$  holds,  $\psi$  is ensured). In particular, this pattern occurs in specifications for safety-critical systems. We will therefore analyze inconsistencies and weaknesses using this specification pattern.

#### 3.5.2 Contract Inconsistencies

Table 3.1 below describes typical inconsistencies between contracts and their underlying detailed models.

| No. | Correct Formula                                     | <b>Inconsistent Formula</b>                           | Description                                                                |

|-----|-----------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------|

| I1  | $\mathbf{G}(\phi \Rightarrow \psi)$                 | $\mathbf{G}(\phi \Rightarrow \psi')$                  | It is erroneously assumed that condition $\phi$ has effect                 |

|     |                                                     |                                                       | $\psi'$ , whereas the real effect expressed in the model is                |

|     |                                                     |                                                       | $\psi$ . Formulas $\psi$ and $\psi'$ only differ in Boolean and/or         |

|     |                                                     |                                                       | arithmetic operators and/or brackets.                                      |

| I2  | $\mathbf{G}(\phi_1 \land \phi_2 \Rightarrow \psi)$  | $\mathbf{G}(\phi_1 \Rightarrow \psi)$                 | A desired effect $\psi$ is assumed to occur already under                  |

|     |                                                     |                                                       | condition $\phi_1$ , while the detailed model only guaran-                 |

|     |                                                     |                                                       | tees $\psi$ if the stronger condition $\phi_1 \wedge \phi_2$ is fulfilled. |

| I3  | $\mathbf{G}(\phi_1 \Rightarrow \psi_1)$             | $\mathbf{G}(\phi_1 \Rightarrow \psi_1 \wedge \psi_2)$ | A pre-condition $\phi_1$ is assumed to achieve a stronger                  |

|     |                                                     |                                                       | effect $\psi_1 \wedge \psi_2$ than what is really guaranteed by the        |

|     |                                                     |                                                       | $\operatorname{model}(\psi_1).$                                            |

| I4  | $\mathbf{G}(\phi_1 \Rightarrow \psi_1 \vee \psi_2)$ | $\mathbf{G}(\phi_1 \Rightarrow \psi_1)$               | It is erroneously assumed that condition $\phi_1$ always                   |

|     |                                                     |                                                       | implies effect $\psi_1$ , whereas the model will only guar-                |

|     |                                                     |                                                       | antee $\psi_1$ to be among the <i>possible</i> effects, so $\psi_2$ may    |

|     |                                                     |                                                       | be observed instead of $\psi_1$ .                                          |

Table 3.1: Typical inconsistencies in LTL contract specifications.

#### 3.5.3 Contract Weaknesses

Table 3.2 describes typical weaknesses of contracts. This means that the contract specification is consistent with the underlying model, but it does not express all the properties which are necessary to prove the global GALS verification goal.

| No. | Correct Formula                                       | Weaker Formula                                        | Description                                                                       |

|-----|-------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------|

| W1  | $\mathbf{G}(\phi \Rightarrow \psi_1 \wedge \psi_2)$   | $\mathbf{G}(\phi \Rightarrow \psi_1)$                 | The model guarantees that $\phi$ will have effects $\psi_1 \wedge$                |

|     |                                                       |                                                       | $\psi_2$ , while the contract only lists the effect $\psi_1$ .                    |

| W2  | $\mathbf{G}(\phi_1 \vee \phi_2 \Rightarrow \psi_1)$   | $\mathbf{G}(\phi_1 \Rightarrow \psi_1)$               | The model guarantees that effect $\psi_1$ will occur if ei-                       |

|     |                                                       |                                                       | ther $\phi_1$ or $\phi_2$ are ensured. The contract, however,                     |

|     |                                                       |                                                       | only captures occurrence of effect $\psi_1$ in case of pre-                       |

|     |                                                       |                                                       | condition $\phi_1$ .                                                              |

| W3  | $\mathbf{G}(\phi_1 \Rightarrow \psi_1)$               | $\mathbf{G}(\phi_1 \wedge \phi_2 \Rightarrow \psi_1)$ | The contract assumes that $\psi_1$ will only occur if both                        |

|     |                                                       |                                                       | $\phi_1$ and $\phi_2$ are fulfilled, while the model already                      |

|     |                                                       |                                                       | guarantees $\psi_1$ to occur if $\phi_1$ holds.                                   |

| W4  | $\mathbf{G}(\phi_1 \Rightarrow \psi_1 \vee \psi_2)$   | $\mathbf{G}(\phi_1 \Rightarrow \psi_1 \vee \psi_2)$   | The contract only expresses (correctly) that condi-                               |

|     | $\mathbf{G}(\phi_1 \wedge \phi_2 \Rightarrow \psi_1)$ |                                                       | tion $\phi_1$ yields effect $\psi_1$ or effect $\psi_2$ . For the global          |

|     | $\mathbf{G}(\phi_1 \wedge \phi_3 \Rightarrow \psi_2)$ |                                                       | GALS verification, however, the stronger properties                               |

|     |                                                       |                                                       | are required, which can guarantee either $\psi_1$ or $\psi_2$                     |

|     |                                                       |                                                       | under stricter conditions $\phi_1 \wedge \phi_2$ and $\phi_1 \wedge \phi_3$ , re- |

|     |                                                       |                                                       | spectively.                                                                       |

Table 3.2: Typical weaknesses in LTL contract specifications.

# **Chapter 4**

# Domain Specific Contract Modeling Language for Users

## 4.1 Objectives

As indicated in Fig. 1.1, the objective of the GALS translation language GTL (Section 5) is to provide a formalism for specification of contracts and system requirements which is close to the level of abstraction required by simulators, verification and test tools. In contrast to this, the **Contract Domain Specific Language (CDSL)** has the goal to facilitate the elaboration of contract networks and system requirements for the end user. The "ingredients" of the CDSL have been identified by analysis of the case studies presented in Sections 12.1 and 12.2 and other embedded system models used by Verified Systems International GmbH for the purpose of testing distributed embedded systems [80, 81]. While the expressive power of the CDSL is equivalent to that of the GTL, the former is syntactically richer, in order to provide adequate representation "instruments" for the different modeling objectives required from the end users' perspective. From the description of the CDSL  $\rightarrow$  GTL transformation in Section 4.5 it will become apparent that these syntactic elements can all be mapped to the structural capabilities, formula and state machine expressions available in the GTL.

The syntactic elements of the CDSL have been motivated by the following insights.

- Some aspects of contracts depend on hidden states. These types of assertions are often more easily expressed by **state machines** than by LTL formulas.

- Though always representable by state machines or LTL formulas, it is often more convenient to specify stateless input-output relationships by means of **decision tables**.

- The efficiency of the verification process on GALS system level is facilitated and made more effective if contracts can optionally express **guaranteed behavior** about local components of the GALS network (see Section 4.3).

- A mixed graphical and textual representation of contract and system specifications is preferred by end users who are often familiar with formalisms like SCADE, UML or Matlab/Simulink.

- Graphical representations should not force users to represent multiple similar nodes and their interfaces in the GALS system network in an explicit way<sup>1</sup>. It is more suitable to depict "representatives" (or, formally, classes) of concrete object and interface collections in the graphical

<sup>&</sup>lt;sup>1</sup>Just as users are reluctant to explicitly represent many instances if the same class in a UML object model.

contract network description and use tabular instantiation rules indicating how the network is unfolded by multiple instantiation of the representatives.

## 4.2 Abstract Language Description

In the following we sketch the CDSL language in more detail. We use EBNF-style<sup>2</sup> notation to explain the syntactic elements. The " $\oplus$ " operator denotes a simple composition of elements.

```

<CONTRACTNETWORK>

::= <CONTRACTNET>

⊕ <INTERFACE><sup>+</sup>

⊕ <CONSTANTDEFINITIONS>

⊕ <Instantiation>

::= \underbrace{< SYNCHRONOUSSTRUCT>^+}_{asynchronously connected} \oplus < CONNECTOR>^*

<CONTRACTNET>

::= (<CONTRACTCLASS> | <COMPOSITESTRUCT>)

<SYNCHRONOUSSTRUCT>

⊕ <GUARANTEEDBEHAVIOUR>*

::= \underbrace{<\text{CONTRACTCLASS}>^+}_{\text{synchronously connected}} \oplus <\text{CONNECTOR}>^*

<COMPOSITESTRUCT>

<CONTRACTCLASS>

::= \langle INPUTVARS \rangle \oplus \langle OUTPUTVARS \rangle \oplus \langle INTERNALVARS \rangle

⊕ <CLASSCONSTRAINT> ⊕ <CONTRACT>

<GUARANTEEDBEHAVIOUR> ::= <LTLFORMULA>

<CLASSCONSTRAINT> ::= <LTLFORMULA>*

::= (<LTLFORMULA> | <STATEMACHINE>)

<CONTRACT>

where

<CONSTANTDEFINITIONS> is a set of symbolic constants (parameters),

is the abstract definition of data flow (structured data),

<INTERFACE>

is a directed arrow associated with an <INTERFACE>,

<CONNECTOR>

<*VARS>

is a set of variables (respectively input, output, or internal),

<STATEMACHINE>

is a state machine description without parallelism, and

<LTLFORMULA>

is one Linear-Time-Logic Formula interpreted over state machine

states and variables

```

Figure 4.1: EBNF-style description of the CDSL, root element is <CONTRACTNETWORK>.

The crucial part of the language definition in Figure 4.1 is that all nodes in a contract net, i.e. the <SYNCHRONOUSSTRUCT> elements, are *asynchronously* connected with each other. One node of the net may be described as a *synchronous* composition of components. The guaranteed behavior is

<sup>&</sup>lt;sup>2</sup>EBNF is a shorthand for Extended Backus-Naur Form, see e.g. [84].

given in form of LTL formulas (e.g. invariants), and can be accumulated (corresponding to logical "and").

A *contract class* follows the class stereotype. The different categories of variables are listed explicitly, since input and output variables correspond to the connectors, i.e., the *interfaces*. The behavioral restriction on a class—i.e., the contract— is made explicit either via an *LTL formula* or a *state machine* definition.

Similar to the contract class, the *interface* is seen as a template, that has to be instantiated appropriately. The *instantiation* commonly defines the concrete instances of classes and interfaces.

**State Machines.** State machines may decompose hierarchically, but without parallelism (architectural hierarchy). States (or super-states) can be annotated with entry- or do-actions, which can be defined either via assignment expressions or via *decision tables* for reasons of brevity.

Transitions can be guarded with boolean expressions that have to evaluate to true in order to enable a transition. The states can be equipped with constraints. A states cannot be entered if this would violate any constraint; a state has to be left if one of the contraints would be violated otherwise.

For our purpose, the state machines are deterministic in the sense that there in any state there is at most one transition that is enabled. If two or more transitions would be enabled according to guards and contraints, then *priorities* associated with transitions resolve this situation deterministically.

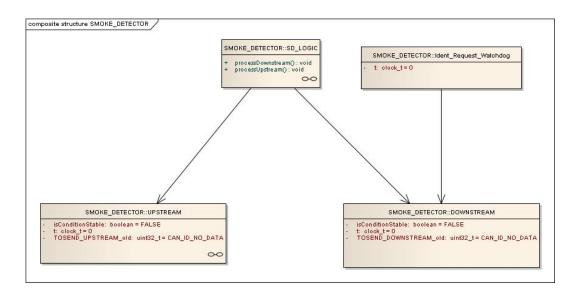

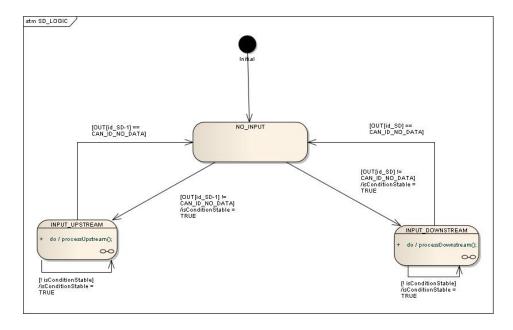

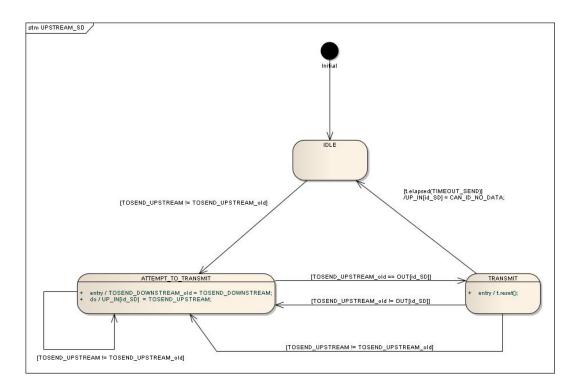

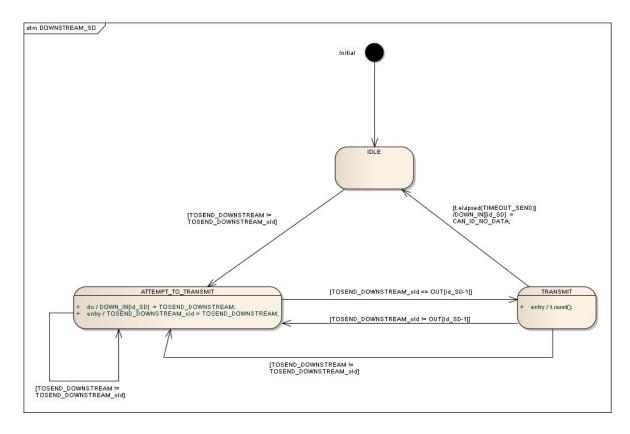

A complete example for the CDSL is given in connection with the case study in Section 12.1, see Figure 12.2 for the <CONTRACTNETWORK>.

## 4.3 Specifying and Exploiting Guaranteed Behavior

#### 4.3.1 Guaranteed Behavior in Contract Specifications

Guaranteed behavior is a part of a contract specification expressing a property P of the local system which has been verified in a trustworthy way so that counter examples occurring during system verification and contradicting P imply that either

- C's contract has not been adequately specified, or,

- another component has previously violated the assumption made by C, so that C is no longer obliged to fulfill its contract.

The concept of guaranteed behavior naturally arises in a scenario where a large GALS system is integrated by a main contractor or system integrator, while the components are provided by different suppliers who have performed thorough verification, validation and test activities on their component, but without consideration of causal dependencies of the global system.

- The integrator specifies the contract network for the GALS system with the objective of GALS system verification. For this purpose the local contracts specified by the integrator for each node may be highly non-deterministic, that is, under-specified. Only those behavioral aspects of each component are captured that seem relevant for the system-level verification.

- The verification results obtained by the sub-contractor may be optionally added to each component's contract as guaranteed behavior to support validation of the contract network.

- Analyzing the guaranteed behavior, integrators may investigate which facts have already been

established on local components, so that they do not have to be re-verified on system level. As

a consequence integrators will direct their system-level verification activities to those which are

not immediate consequences of guaranteed behaviors.

- If system-level verification implies the existence of system computations (arising, for example, from counter examples produced by a model checking tool) contradicting one or more guaranteed behavior assertions, integrators can conclude that their network of contracts has been inadequately specified (cf. the discussion in Section 3.4).

These aspects of guaranteed behavior utilization during system-level verification are explained in more detail in the sections to follow.

#### 4.3.2 Patterns of Guaranteed Behavior

Guaranteed behavior may be based on

- formal verification of component models or/and component code, and,

- tests that have been performed with the software or with the integrated HW/SW system and that have passed their evaluation criteria.

When focusing on safety properties, the former case may be typically expressed by LTL properties of the form

$$\mathbf{G}(\phi \Rightarrow \psi)$$

("Whenever condition  $\phi$  is fulfilled in a state of component C, the component will ensure  $\psi$ "). The latter case is typically represented by formulas of the form

$$\mathbf{F}(\phi \wedge \psi)$$

("Finally the pre-condition  $\phi$  for the given test purpose has been reached, and from there on the expected reaction  $\psi$  of C could be observed").

In many situations the application of the equivalence class principle can be applied, so that *all* system states fulfilling some condition  $\phi$  are adequately represented by the set of system states fulfilling  $\phi_1, \ldots, \phi_k$  which have been visited during the tests for the objectives  $\mathbf{F}(\phi_i \wedge \psi_i), i = 1, \ldots, k$ . If this is the case,

$$\bigwedge_{i=1}^{k} (\phi_i \Rightarrow \phi)$$

holds<sup>3</sup>. If the results  $\psi_i$  obtained in these tests are consistent with  $\psi$ , that is,

$$\bigwedge_{i=1}^{k} (\psi_i \Rightarrow \psi)$$

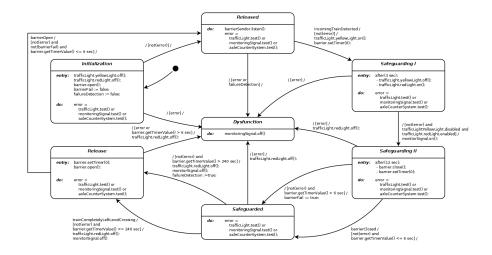

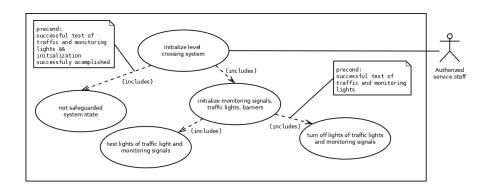

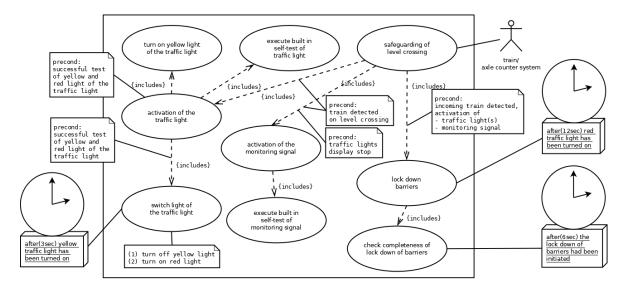

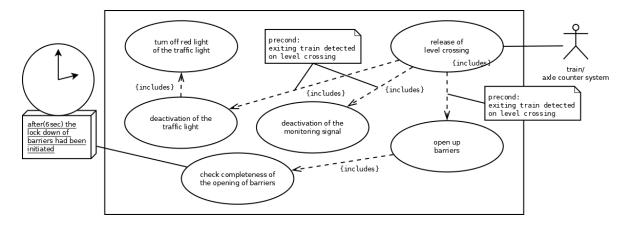

it is admissible, according to existing standards for safety-critical systems verification, to assume that also  $\mathbf{G}(\phi \Rightarrow \psi)$  is guaranteed behavior, established by these tests.